# **CMOSTEK**

# **CMT2300A FIFO and Packet Format Usage Guideline**

#### Summary

This article describes the CMT2300A FIFO, packet format and the working principle of the interrupt system. When the article introduces the contents of the configuration register, it will correspond to the parameters that can be entered on the RFPDK to facilitate the user configuration.

The part numbers covered by this document are as shown below.

#### Table1. Part Numbers Covered by This Document

| Part No. | Frequency     | Modem      | Function    | Configuration | Package |

|----------|---------------|------------|-------------|---------------|---------|

| CMT2300A | 127 - 1020MHz | (G)FSK/OOK | Transceiver | Register      | QFN16   |

Before reading this document, it is recommended that reading the «AN142 - CMT2300A Quick Start Guideline», that will be make it easy to understand.

# Table of contents

| Sum | nmary  |          |                                                                                      | 1  |

|-----|--------|----------|--------------------------------------------------------------------------------------|----|

| 1.  | FIFO \ | Norking  | g Principle                                                                          | 3  |

|     | 1.1    | FIFO R   | elated Register                                                                      | 3  |

|     | 1.2    | FIFO V   | Vorking Mode                                                                         | 5  |

|     | 1.3    | FIFO II  | nterrupt Timing                                                                      | 7  |

|     | 1.4    | FIFO A   | pplication Scenes                                                                    | 7  |

|     | 1      | .4.1     | Application scene 1: Receive the data at RX                                          | 8  |

|     | 1      | .4.2     | Application scene 2: Fill in the data beforehand and enter the TX transmitting       | 8  |

|     | 1      | .4.3     | Application scene 3: After entering the TX, fill in the data while transmitting them | 9  |

|     | 1      | .4.4     | Application scene 4: Send repeatedly the same or same set of packets each time       | 9  |

|     |        | .4.5     | Application scene 5: A packet is sent several times apart                            |    |

| 2.  | Packe  |          | at Introduction                                                                      |    |

|     | 2.1    |          | Mode Configuration                                                                   |    |

|     | 2.2    |          | ble Configuration                                                                    |    |

|     | 2.3    |          | Nord Configuration                                                                   |    |

|     | 2.4    | Packet   | t Overall Configuration                                                              | 15 |

|     | 2.5    | Node     | ID Configuration                                                                     | 17 |

|     | 2.6    | FEC Co   | onfiguration                                                                         | 21 |

|     | 2.7    | CRC C    | onfiguration                                                                         | 22 |

|     | 2.8    | Codec    | Configuration                                                                        | 24 |

|     | 2.9    | Tx Pac   | ket Specific Configuration                                                           | 26 |

|     | 2.10   |          | Tx Mode                                                                              |    |

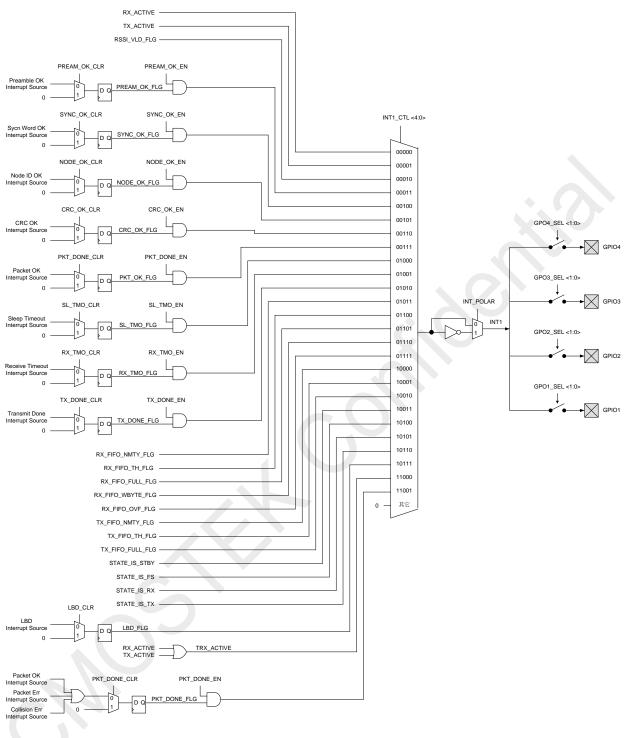

| 3.  | GPIO   | and Inte | errupt                                                                               | 28 |

|     | 3.1    | GPIO (   | Configuration                                                                        | 28 |

|     | 3.2    | Interr   | upt Configuration and Mapping                                                        | 29 |

|     | 3.3    | Anten    | na TX / RX Switching Control                                                         | 36 |

| 4.  | Docur  | ment M   | odification Record                                                                   | 37 |

| 5.  | Conta  | ct Infor | mation                                                                               | 40 |

# 1. FIFO Working Principle

# 1.1 FIFO Related Register

The corresponding RFPDK interface and parameters are as below:

| peration Settings             | OOK Demod Settings | (G)FSK Demod Settings | Baseband 1 Settings | Baseband 2 Settings  | Feature Settings   |                 |

|-------------------------------|--------------------|-----------------------|---------------------|----------------------|--------------------|-----------------|

| Baseband Setting<br>Data Mode | 2000 C             |                       |                     |                      |                    | ]               |

| Packet                        | *                  |                       |                     |                      |                    | List            |

| Whitening                     |                    | Whiten Type           | in.                 | hiten Seed Type      | Whiten Seed (0-51  | 11)             |

| Disable                       |                    | NA =                  |                     | NA -                 | NA                 | Export          |

| Mancheste                     | er                 | Manchester Type       | FI                  | EC                   | FEC Type           |                 |

| Disable                       | •                  | NA *                  |                     | Disable              | NA ~               | Burn            |

| Tx Prefix T                   | ype                | Tx Packet Number (1   | 1-256) T            | x Packet Gap (2-256) | Fifo Threshold (1- | -31)            |

| 0                             | *                  | 1                     |                     | 32                   | 16                 |                 |

| USB:Unconnected               | d 🕘 Device: U      | nknown Notice:        |                     |                      |                    | www.cmostek.com |

#### **Table 2. FIFO Related Parameter**

| Register Bit RFPDK Parameter                                       | Register Bit     |

|--------------------------------------------------------------------|------------------|

| Data Mode                                                          | DATA_MODE <1:0>  |

| RFPDK does not display the parameter and it is flexibly configured | FIFO_TH <6:0>    |

| by the user in the application.                                    |                  |

| The parameter is automatically calculated based on the TX packet   | FIFO_AUTO_RES_EN |

| number. When the TX packet number is greater than 1, the           |                  |

| parameter is set to 1.                                             |                  |

The contents and explanations of the register can be seen in the following table.

#### Table 3. Register Located in the Configuration Bank:

| Register<br>Name | Bits | R/W | Bit Name         | Function Description                                                                                                                                                                                                               |

|------------------|------|-----|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CUS_PKT1         | 1:0  | RW  | DATA_MODE <1:0>  | Data processing mode:<br>0: Direct Mode (Default)<br>1: NA                                                                                                                                                                         |

| (0x38)           |      |     |                  | 2: Packet Mode<br>3: NA                                                                                                                                                                                                            |

| CUS_PKT29        | 7    | RW  | FIFO_AUTO_RES_EN | Each time it sends a package, it automatically<br>restores TX FIFO. If you enter TX each time to<br>send repeatedly more than 1 packet<br>(TX_PKT_NUM> 0), this bit must be set to 1.                                              |

| (0x54)           | 6:0  | RW  | FIFO_TH <6:0>    | FIFO threshold, the unit is byte. For RX, when<br>the unread data exceeds this threshold, the<br>RX_FIFO_TH_FLG will be set to 1. For TX,<br>when no sending data is less than this<br>threshold, TX_FIFO_TH_FLG will be set to 0. |

| Register<br>Name | Bits | R/W | Bit Name | Function Description                                                                                                     |

|------------------|------|-----|----------|--------------------------------------------------------------------------------------------------------------------------|

|                  |      |     |          | When FIFO_MERGE_EN = 0, the effective<br>range is 1 to 31.<br>When FIFO_MERGE_EN = 1, the effective<br>range is 1 to 63. |

# Table 4. Register Located in the Control Bank 1

| Register     | Bits | R/W | Bit Name           | Function Description                                  |

|--------------|------|-----|--------------------|-------------------------------------------------------|

| Name         |      |     |                    |                                                       |

|              | _    |     |                    | 0: Automatically clear RX FIFO before entering        |

|              | 4    | RW  | FIFO_AUTO_CLR_DIS  | RX.                                                   |

|              |      |     |                    | 1: No auto clear.                                     |

|              |      |     |                    | 0: TX FIFO can only be written by SPI.                |

|              | 3    |     | FIFO_TX_RD_EN      | 1: RX FIFO can be read by SPI. This bit is valid      |

|              | 3 F  | RW  |                    | only for TX FIFO, Except that it is available for     |

| CUS_FIFO_CTL |      |     |                    | user testing, the bit should be set to 0 at the rest. |

|              |      |     | FIFO_RX_TX_SEL     | As a 64-byte FIFO, it can be used.                    |

| (0x69)       | 2    | RW  |                    | 0: Used for RX FIFO;                                  |

|              |      |     |                    | 1: Used for TX FIFO。                                  |

|              | 1    |     |                    | 0: The FIFO is divided into 2 separate 32-byte;       |

|              |      | RW  | FIFO_MERGE_EN      | 1: Merge into one 64-byte FIFO.                       |

|              |      |     |                    | 0: The operation of SPI is to read FIFO;              |

|              | 0    | RW  | SPI_FIFO_RD_WR_SEL | 1: The operation of SPI is to write FIFO. You         |

|              |      |     |                    | must set it up before you visit FIFO.                 |

# Table 5. Register Located in the Control Bank 2

| Register Name | Bits | R/W | Bit Name     | Function Description                              |

|---------------|------|-----|--------------|---------------------------------------------------|

|               |      |     |              | Users restore TX FIFO manually. Restore           |

|               |      |     |              | means resetting the read pointer. Keep the        |

|               | 2    | W   | FIFO_RESTORE | write pointer unchanged, so that TX FIFO is       |

|               |      |     |              | returned to unread state, and you can             |

|               |      |     |              | repeatedly send the data filled before.           |

|               |      |     |              | 0: Invalid,                                       |

| CUS_FIFO_CLR  |      | 1 W | FIFO_CLR_RX  | 1: Clear RX FIFO。                                 |

| (0x6C)        | 1    |     |              | After the user has set this bit to 1, it does not |

|               |      |     |              | need to be set to 0 again, and this bit is        |

|               |      |     |              | automatically set back to 0 inside.               |

|               |      |     |              | 0:: Invalid,                                      |

|               | 0    |     |              | 1: Clear TX FIFO                                  |

|               | 0    | W   | FIFO_CLR_TX  | After the user has set this bit to 1, it does not |

|               |      |     |              | need to be set to 0 again, and this bit is        |

|                         |   |   |                  | automatically set back to 0 inside.                                                                          |

|-------------------------|---|---|------------------|--------------------------------------------------------------------------------------------------------------|

|                         | 6 | R | RX_FIFO_FULL_FLG | Indicates the interrupt flag bit that RX FIFO is<br>full.<br>0: Invalid<br>1: Valid                          |

|                         | 5 | R | RX_FIFO_NMTY_FLG | Indicates the interrupt that the unread<br>contents of RX FIFO exceed the FIFO TH.<br>0: Invalid<br>1: Valid |

|                         | 4 | R | RX_FIFO_TH_FLG   | Indicates the interrupt that RX FIFO is filled.<br>0: Invalid<br>1: Valid                                    |

| CUS_FIFO_FLAG<br>(0x6E) | 3 | R | RX_FIFO_OVF_FLG  | Indicates the interrupt that RX FIFO<br>overflows.<br>0: Invalid<br>1: Valid                                 |

|                         | 2 | R | TX_FIFO_FULL_FLG | Indicates the interrupt that TX FIFO is full.<br>0: Invalid<br>1: Valid                                      |

|                         | 1 | R | TX_FIFO_NMTY_FLG | Indicates the interrupt that the unread<br>contents of TX FIFO exceed the FIFO TH.<br>0: Invalid<br>1: Valid |

|                         | 0 | R | TX_FIFO_TH_FLG   | Indicates the interrupt that TX FIFO is filled.<br>0: Invalid<br>1: Valid                                    |

The polarity of these interrupt flag bits is controlled by the INT\_POLAR. That is, when INT\_POLAR = 1, they are all 0 valid and 1 invalid.

In these registers, some bits that are not associated with the FIFO are ignored here and are not introduced.

# 1.2 FIFO Working Mode

CMT2300A provides two separated 32-byte FIFO by default. They are used for RX and TX respectively, both are separated each other. Users can also set FIFO\_MARGE\_EN to 1, and then the two FIFO are merged into a 64-byte FIFO. It can be used both under TX and RX. By configuring the FIFO\_RX\_TX\_SEL to indicate whether it is currently used as TX or RX.

In general, we would suggest that the FIFO working mode is pre configured in the STBY state, and then starting the work of TX/RX. As long as the registers locate in the configuration bank and the control bank 1, the contents can be saved in the SLEEP state. Therefore, unless you change your working mode, configuring once is enough.

# Separate FIFO pre configuration

- 1. Set DATA\_MODE <1:0> to 2 and set the data processing mode to Packet mode.

- 2. Set FIFO\_MERGE\_EN to 0.

- 3. Select the operation to be performed afterwards:

If you want to go to RX:

- a) Configure SPI\_FIFO\_RD\_WR\_SEL to 0 (SPI read FIFO mode);

- b) If the user wants RX FIFO to be automatically cleared every time he enters the RX, the FIFO\_AUTO\_CLR\_DIS is set to 0, otherwise it is set to 1, and then manually cleared.

If you want to go to TX:

a) Configure SPI\_FIFO\_RD\_WR\_SEL to 1 (SPI write FIFO mode)

#### Merged FIFO pre configuration

- 1. Set DATA\_MODE <1:0> to 2 and set the data processing mode to Packet mode.

- 2. Set FIFO\_MERGE\_EN to 1.

- 3. Select the operation to be performed afterwards:

If you want to go to RX:

- a) Set FIFO\_RX\_TX\_SEL to 0 (RX mode);

- b) Configure SPI\_FIFO\_RD\_WR\_SEL to 0 (SPI read FIFO mode);

- c) If the user wants RX FIFO to be automatically cleared every time he enters the RX, the FIFO\_AUTO\_CLR\_DIS is set to 0, otherwise it is set to 1, and then manually cleared before starting.

If you want to go to TX:

- a) Set FIFO\_RX\_TX\_SEL to 1 (TX mode);

- b) Configure SPI\_FIFO\_RD\_WR\_SEL to 1 (SPI write FIFO mode)..

- c) Clear manually before starting.

When FIFO is merged, there is only one FIFO inside the chip. Because RX/TX is half duplex, one FIFO is enough. When FIFO is divided into two, they are independent of each other, and without interference, some special functions can be realized. For example, if the transmitting data is the same every time, and the RX FIFO can save the contents under SLEEP, then the TX FIFO will only need to be filled once to save time and power. Another example is that the RX FIFO is written continuously in the RX state, and the user can use the received time to fill the data to be transmitted next time into the TX FIFO in parallel. This will not disturb the work of RX FIFO, but also save time. And also this will not leave the special time to fill in the TX FIFO, but also save the power.

It is important to note that you must clear manually after you switch between TX FIFO and RX FIFO each time, otherwise it will not work properly.

In order to apply to the FIFO merging and not merging the two cases, FIFO read-write enable operations configure FIFO\_RX\_TX\_SEL and SPI\_FIFO\_RD\_WR\_SEL according to the merging usage requirements.

Cmt2300\_GoStby(); Cmt2300\_ClearInterruptFlags(); /\* Must clear FIFO after enable SPI to read or write the FIFO \*/ Cmt2300\_EnableWriteFifo(); Cmt2300\_ClearFifo(); // When merged FIFO is used, additional delay is required when the sending byte is too long. /\* The length need be smaller than 32 \*/ Cmt2300\_WriteFifo(g\_pTxBuffer, g\_nTxLength);

FIFO read-write operation code examples see Appendix 1.

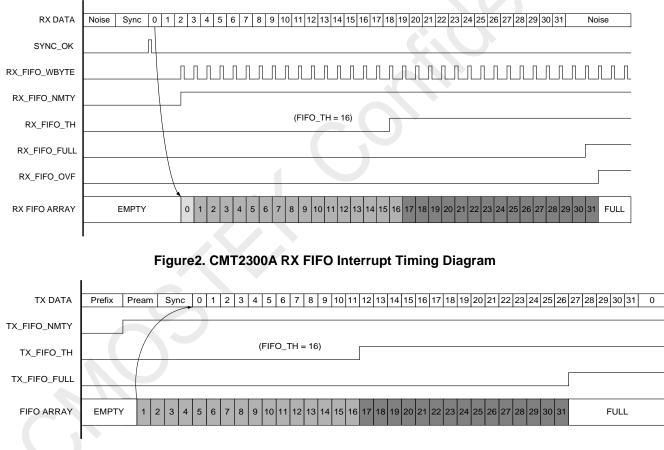

# 1.3 FIFO Interrupt Timing

Here, we first give the interrupt timing diagram of RX FIFO and TX FIFO. Users can refer to them to understand easily.

Figure 3. CMT2300A TX FIFO Interrupt Timing Diagram

# 1.4 FIFO Application Scenes

When the FIFO is configured, you can start using it. Here are some classic application scenes. To complete the entire process of TX and RX, you also need to configure and control other things. These are introduced later. Here we will only introduce the contents related to FIFO.

#### 1.4.1 Application scene 1: Receive the data at RX

RX FIFO is used more directly. Clear it when you enter RX every time. Enter RX and fill them if the data is received (Detect the Sync Word successfully). MCU can achieve the following several operations according to the interrupt. After you have finished, you cannot use it. Send FIFO\_CLR\_RX to clear before you receive it next time.

- 1. Detect the RX\_FIFO\_FULL interrupt. Once valid indicates that the FIFO has been filled, you can start reading. The appropriate packet length is just equal to the FIFO depth. Also, the user does not read the FIFO until the full packet is received.

- 2. Detect the RX\_FIFO\_TH interrupt. Once valid indicates that the FIFO has been filled in the preset data length, you can start reading. The appropriate packet length is not equal to the FIFO depth. Also, the user does not read the FIFO until the full packet is received.

- 3. Detect the RX\_FIFO\_NMTY interrupt. Once valid, read immediately until the interrupt is invalid. Read again when the interrupt is valid again. This allows you to read them while you receive them. It is suitable for the case where the packet length is greater than the FIFO depth and is suitable for the case where the packet length or the FIFO depth.

- 4. Detect the X\_FIFO\_WBYTE interrupt. Read immediately once it is valid. This allows you to achieve the regular operation to write a byte and then read a byte. The premise is that SPI is faster than receiving the data.

In addition, you can define how many packets are sent per sending by setting the TX\_PKT\_NUM <7:0>. If sending the packet is more than one, the FIFO\_AUTO\_RES\_EN is set to 1. That is, the TX FIFO automatically clears the read pointer and goes back the unread state after each packet is sent. This allows you to repeatedly send the same packet. You don't need MCU to fill in the data again. The user can set the TX\_PKT\_GAP <7:0> to define the time gap between each packet, the unit is the symbol. After entering the transmitting state, the transmitter sends N packets according to these configurations. After completing, the transmitter automatically exits the TX and returns to the specified state. The status after exiting can be configured by TX\_EXIT\_STATE <1:0>.

If you want to achieve continuous reception, it is recommended to use the above fourth operation. This needs SPI to read quickly enough. At least it is 1.5 times faster than the rate that FIFO writes a byte. For example, if the data rate is 10KHz, the time it takes to receive a byte is about 800 us. The rate SPI reads a byte is 1.5 times faster than the rate FIFO writes a byte. The most time-consuming is 534us. SPI reads a byte for 8 SCL clock cycles, but with the added time cost before and after, we can count it according to the 10 SCL clock cycles, then each cycle is 53.4us, converted to SCL clock frequency is about 18.7 kHz. The rate of SCL is roughly 2 times the rate of data.

#### 1.4.2 Application scene 2: Fill in the data beforehand and enter the TX transmitting

For many applications, pre fill the data packets to be transmitted into TX FIFO, and then enter the TX transmitting. The behavior of filling data is suggested to be executed in the STBY state. This scene is suitable for packet length less than or equal to FIFO depth, and the application time does not need to be very compact. After the user pre configured, he can write the data directly and judge whether the data has been fully written by detecting the interrupt of TX\_FIFO\_NMTY, TX\_FIFO\_TH or TX\_FIFO\_FULL. During the debugging stage, after completing the data, the user can read back the filling data according to the following methods, and

confirm whether the filling data is the correct:

- 1. Set FIFO\_TX\_RD\_EN to 1 and enter the read back mode of TX FIFO.

- 2. Set SPI\_FIFO\_RD\_WR\_SEL to 0 and enter the read FIFO mode of SPI.

- 3. Read the data and confirm whether it is correct.

- 4. Set FIFO\_TX\_RD\_EN to 0 and exit the read back mode of TX FIFO.

- 5. Set SPI\_FIFO\_RD\_WR\_SEL to 1 and enter the write FIFO mode of SPI.

- 6. Set FIFO\_CLR\_TX to 1 and clear FIFO.

- 7. Re write the data to be ready for transmitting.

# 1.4.3 Application scene 3: After entering the TX, fill in the data while transmitting them.

If the user first enters the TX state, but the TX FIFO is empty, the chip will always transmit the prefix. The content of the prefix is determined by TX\_PREFIX\_TYPE <1:0>, which can be 0, 1, or preamble. At the time of transmitting the prefix, the chip will have been waiting for the user to fill FIFO, until the user begin to fill in the first data byte, the chip will stop transmitting the prefix, and has been according to the rhythm of the data rate to obtain FIFO data to transmit them until the end. So in this scene, SPI is fast enough, and SCL is at least 2 times as fast as the data rate. If the speed of SPI writing cannot catch up during the transmitting data, that is, the FIFO is read out by the transmitter, transmitting will not stop, and will always send 0 until FIFO fill in the next data. But this is an improper operation, and the user should try to avoid it.

# 1.4.4 Application scene 4: Send repeatedly the same or same set of packets each time

Since TX FIFO saves the content in the SLEEP state, MCU just needs to fill in the data once if the data sent each time is the same. After completing the sending each time, enter STBY and set FIFO\_RESTORE to 1 (Without setting 0, this bit will be cleared automatically), clear the FIFO read pointer. This means that FIFO is back in the unread state, and the data is stored in it. Entry TX next time and re send the same content, go round and begin again. If FIFO\_AUTO\_RES\_EN has been set to 1, you don't have to manually set FIFO\_RESTORE, and next time you go directly to the TX to send them.

# 1.4.5 Application scene 5: A packet is sent several times apart

TX FIFO not only saves the content in the SLEEP state, but also saves the pointer state. For example, with the merged FIFO, the size is 64-byte, and the user will send the four packets one after another, each packet is 16-byte. Then, users can first fill these 4 packets in FIFO in STBY, and make sure that FIFO is full, then set the data length to 16 (how to set it according to the packet format, the following will introduce.), set the TX packet number to 1, set the FIFO\_AUTO\_RES\_EN to 0, and then enter the TX. The chip sends the first 16-byte packet, exit to STBY after completing, and then re-enter the TX, the chip sends the second packet..... until the fourth sending is completed. In this process, MCU does not need to do anything. It is only responsible for detecting the interrupt and switching the state.

# 2. Packet Format Introduction

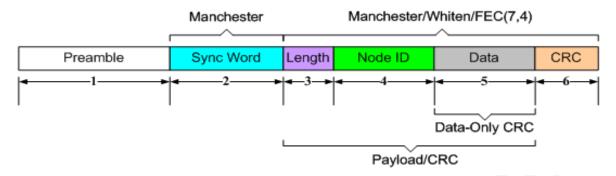

CMT2300A uses the TX and RX unified configuration. It is more typical and more flexible packet format. The structure diagram is as follows:

# Figure 4. Packet Structure Diagram

The packet format contains six optional parts. This structure can meet the demand of most single Field structures in the market, and is not compatible with multi Field structure.

The configurable content of packet format is centered on "the baseband zone". The following will combine these registers to explain how to configure each part.

#### 2.1 Data Mode Configuration

Data Mode refers to the external MCU to input the sending data or obtain the received data by which mode.

#### The corresponding RFPDK interface and parameters are as below:

| peration Settings | OOK Demod Settings | (G)FSK Demod Settings | Baseband 1 Settings | Baseband 2 Settings | Feature Settings      |                 |

|-------------------|--------------------|-----------------------|---------------------|---------------------|-----------------------|-----------------|

| Baseband Settings |                    |                       |                     |                     |                       |                 |

| Data Mode         |                    |                       |                     |                     |                       |                 |

| Packet            | *                  |                       |                     |                     |                       | List            |

| Whitening         |                    | Whiten Type           | W                   | hiten Seed Type     | Whiten Seed (0-511)   |                 |

| Disable           |                    | NA *                  |                     | NA -                | NA                    | Export          |

| Manchester        |                    | Manchester Type       | FE                  | C                   | FEC Type              |                 |

| Disable           | -                  | NA 👻                  |                     | Disable *           | NA -                  | Burn            |

| Tx Prefix Typ     | pe                 | Tx Packet Number (    | (1-256) Ta          | Packet Gap (2-256)  | Fifo Threshold (1-31) | )               |

| 0                 | •                  | 1                     |                     | 32                  | 16                    |                 |

| USB:Unconnected   | Device: Un         | nknown Notice:        |                     |                     |                       | www.cmostek.com |

Figure 5. Data Mode RFPDK Interface

#### Table 6. Data Mode Related Parameter

| Register Bit RFPDK Parameter                                                | Register Bit    |

|-----------------------------------------------------------------------------|-----------------|

| Data Mode                                                                   | DATA_MODE <1:0> |

| Automatically select according to Data Mode. When Data Mode is Direct,      | TX_DIN_SOURCE   |

| input directly the data from GPIO, and when Data Mode is Packet, obtain the |                 |

| data from TX FIFO.                                                          |                 |

| Register<br>Name   | Bits | R/W | Bit Name       | Function Description                                                                                                     |

|--------------------|------|-----|----------------|--------------------------------------------------------------------------------------------------------------------------|

| CUS_PKT1<br>(0x38) | 1:0  | RW  | DATA_MODE<1:0> | Select the Tx/Rx data mode:<br>0: Direct Mode (default)<br>1: NA<br>2: Packet Mode<br>3: NA                              |

| CUS_TX1<br>(0x55)  | 2    | RW  | TX_DIN_SOURCE  | Select the Tx data source location:<br>0: TX data is obtained from TX FIFO<br>1: TX data is input directly from the GPIO |

| Table 7. Register Located in the Configuration Bar | nk |

|----------------------------------------------------|----|

|----------------------------------------------------|----|

The difference between data mode is that:

- Direct –Direct mode. The RX mode only supports the preamble and sync detection. FIFO doesn't work. RX does not support any packet formats.

- **Packet** –Packet format mode. It supports all packet format configurations, FIFO works.

# 2.2 Preamble Configuration

The corresponding RFPDK interface and parameters are as below:

|             | OXAA-         | 0x1234 | -0x00   | 1 byte | Variable | None |     |

|-------------|---------------|--------|---------|--------|----------|------|-----|

| Packet Type | Preamble      | Sync   | Node ID | Length | Data     | CRC  | Lis |

|             | Preamble Unit | t      |         |        |          |      | Bur |

Figure 6. Preamble RFPDK Interface

#### Table 8. Preamble Related Parameter

| Register Bit RFPDK Parameter | Register Bit        |

|------------------------------|---------------------|

| Preamble Rx Size             | RX_PREAM_SIZE<4:0>  |

| Preamble Tx Size             | TX_PREAM_SIZE<15:0> |

| Preamble Unit                | PREAM_LENG_UNIT     |

| Preamble Value               | PREAM_VALUE<7:0>    |

| Register<br>Name   | Bits | R/W | Bit Name            | Function Description                                                                                                                                                                                                      |

|--------------------|------|-----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CUS_PKT1<br>(0x38) | 7:3  | RW  | RX_PREAM_SIZE<4:0>  | <ul> <li>RX mode Preamble length, can be configured to be 0-31 units in length.</li> <li>0: Indicates not to detect Preamble.</li> <li>1 Indicates to detect Preamble of 1 unit of length.</li> <li>And so on.</li> </ul> |

|                    | 2    | RW  | PREAM_LENG_UNIT     | <ul><li>The unit of length of Preamble, shared by TX and RX:</li><li>0: The unit is 8bits.</li><li>1: The unit is 4 bits.</li></ul>                                                                                       |

| CUS_PKT2<br>(0x39) | 7:0  | RW  | TX_PREAM_SIZE<7:0>  | TX mode Preamble length, can be configured to be 0-65535 units in length.                                                                                                                                                 |

| CUS_PKT3<br>(0x3A) | 7:0  | RW  | TX_PREAM_SIZE<15:8> | 0 Indicates not to send Preamble,<br>1 Indicates to send Preamble of 1 unit of<br>length.<br>And so on                                                                                                                    |

| CUS_PKT4<br>(0x3B) | 7:0  | RW  | PREAM_VALUE<7:0>    | Preamble value, shared by TX and RX:<br>8bit is valid when PREAM_LEN_UNIT =0.<br>Only <3:0> is valid when<br>PREAM_LEN_UNIT =1.                                                                                           |

For RX, the Preamble detection success will generate PREAM\_OK interrupt. In addition, Preamble detection will continue throughout the receiving phase, and it is recommended that the user only detect the interrupt when necessary.

# 2.3 Sync Word Configuration

The corresponding RFPDK interface and parameters are as below:

|                                                         | -OxAA                   | -0x1234 | 0x00    | 1 byte | Variable | None |     |

|---------------------------------------------------------|-------------------------|---------|---------|--------|----------|------|-----|

| Packet Type                                             | Preamble                | Sync    | Node ID | Length | Data     | CRC  | Lis |

| First Node, then Len:  Payload Bit Order Start from msb | Sync Manch<br>Disable - |         |         |        |          |      | Bur |

# Table10. Sync Word Related Parameter

| Register Bit RFPDK Parameter | Register Bit     |

|------------------------------|------------------|

| Sync Size                    | SYNC_SIZE<2:0>   |

| Sync Value                   | SYNC_VALUE<63:0> |

| Sync Tolerance               | SYNC_TOL<2:0>    |

| Sync Manch                   | SYNC_MAN_EN      |

|                     |      | Tab | ble11. Register Located in | Configuration Bank                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------|------|-----|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register<br>Name    | Bits | R/W | Bit Name                   | Function Description                                                                                                                                                                                                                                                                                                                                                                                          |

|                     | 6:4  | RW  | SYNC_TOL<2:0>              | <ul> <li>Fault tolerant bits of detecting Sync Word in<br/>RX mode:</li> <li>0: No permit the error.</li> <li>1: Permit 1bit received error.</li> <li>2: Permit 2bits received error.</li> <li>3: Permit 3bits received error.</li> <li>4: Permit 4bits received error.</li> <li>5: Permit 5bits received error.</li> <li>6: Permit 6bits received error.</li> <li>7: Permit 7bits received error.</li> </ul> |

| CUS_PKT5<br>(0x3C)  | 3:1  | RW  | SYNC_SIZE<2:0>             | Sync Word length:<br>0: 1 byte<br>1: 2 bytes<br>2: 3 bytes<br>3: 4 bytes<br>4: 5 bytes<br>5: 6 bytes<br>6: 7 bytes<br>7: 8 bytes                                                                                                                                                                                                                                                                              |

|                     | 0    | RW  | SYNC_MAN_EN                | Sync Word Manchester codec enable:<br>0: Disable<br>1: Enable                                                                                                                                                                                                                                                                                                                                                 |

| CUS_PKT6<br>(0x3D)  | 7:0  | RW  | SYNC_VALUE<7:0>            | Sync Word value, according to different<br>SYNC_SIZE settings to fill in different                                                                                                                                                                                                                                                                                                                            |

| CUS_PKT7<br>(0x3E)  | 7:0  | RW  | SYNC_VALUE<15:8>           | registers, see the following table.                                                                                                                                                                                                                                                                                                                                                                           |

| CUS_PKT8<br>(0x3F)  | 7:0  | RW  | SYNC_VALUE<23:16>          |                                                                                                                                                                                                                                                                                                                                                                                                               |

| CUS_PKT9<br>(0x40)  | 7:0  | RW  | SYNC_VALUE<31:24>          |                                                                                                                                                                                                                                                                                                                                                                                                               |

| CUS_PKT10<br>(0x41) | 7:0  | RW  | SYNC_VALUE<39:32>          |                                                                                                                                                                                                                                                                                                                                                                                                               |

# Table11. Register Located in Configuration Bank

| Register<br>Name | Bits | R/W | Bit Name          | Function Description |

|------------------|------|-----|-------------------|----------------------|

| CUS_PKT11        | 7:0  | RW  | SYNC_VALUE<47:40> |                      |

| (0x42)           | 7.0  |     | STNC_VALUE<47.40> |                      |

| CUS_PKT12        | 7:0  | RW  | SYNC VALUE<55:48> |                      |

| (0x43)           | 7.0  | RVV | STNC_VALUE<00.40> |                      |

| CUS_PKT13        | 7:0  | RW  | SYNC VALUE<63:56> |                      |

| (0x44)           | 7.0  | RVV | STNC_VALUE<03.30> |                      |

|           |              |              |              | SYNC_        | VALUE        |              |              |              |

|-----------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| SYNC_SIZE | <63:56>      | <55:48>      | <47:40>      | <39:32>      | <31:24>      | <23:16>      | <15:8>       | <7:0>        |

| 0         | $\checkmark$ |              |              |              |              |              |              |              |

| 1         | $\checkmark$ | $\checkmark$ |              |              |              |              |              |              |

| 2         | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |              |              |

| 3         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |              |

| 4         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |

| 5         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |

| 6         | $\checkmark$ |              |

| 7         | $\checkmark$ |

The tick in the table indicates the register to be filled in. For example, if SYNC\_SIZE is set to 1, the length is 2 bytes, the synchronous word is 0x5678, then the user will fill the value in the two registers of SYNC\_VALUE<63:56> and SYNC\_VALUE<55:48>. The MSB corresponds to the sixty-third bit. The LSB corresponds to the forty-eighth bit. That is filling 0x56 into SYNC\_VALUE<63:56> and filling 0x78 into SYNC\_VALUE<55:48>.

In addition, some applications need to Manchester encode the entire packet, but most applications only need to encode Payload. So, design a Manchester encoding enable bit alone for Sync Word.

# 2.4 Packet Overall Configuration

The corresponding RFPDK interface and parameters are as below:

| aseband2 Settings                                                                                                                                          |                                                                                             |                                                                         |                                                                           |                  |             |                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------|-------------|-----------------|

|                                                                                                                                                            | DxAA                                                                                        | 0x1234                                                                  | 0x00                                                                      |                  | None        | ¬               |

| Packet Type                                                                                                                                                | Preamble                                                                                    | Sync                                                                    | Node ID                                                                   | Data             | CRC         | List            |

| Fixed Length                                                                                                                                               |                                                                                             |                                                                         |                                                                           |                  |             |                 |

| Node-Length Position                                                                                                                                       |                                                                                             |                                                                         |                                                                           |                  |             | Expor           |

| NA -                                                                                                                                                       | Length (1-2048)                                                                             | 32                                                                      |                                                                           |                  |             |                 |

| Payload Bit Order                                                                                                                                          |                                                                                             |                                                                         |                                                                           |                  |             | Burn            |

| Start from msb 💌                                                                                                                                           |                                                                                             |                                                                         |                                                                           |                  |             |                 |

|                                                                                                                                                            |                                                                                             |                                                                         |                                                                           |                  |             |                 |

| USB:Unconnected                                                                                                                                            | Device: Unknown                                                                             | Notice:                                                                 |                                                                           |                  | [           | www.cmostek.com |

| USB:Unconnected Oracle Action Settings OOK Demod aseband2 Settings                                                                                         | Settings (G)FSK Demod :                                                                     | Settings Baseband 1 Settin                                              |                                                                           | Feature Settings |             | www.cmostek.com |

| ration Settings OOK Demod<br>aseband2 Settings                                                                                                             | Settings (G)FSK Demod                                                                       | Settings Baseband 1 Setting                                             | -0x00                                                                     | Variable         | None        |                 |

| ration Settings OOK Demod<br>aseband2 Settings                                                                                                             | Settings (G)FSK Demod :                                                                     | Settings Baseband 1 Setting                                             | •                                                                         | Variable         | None<br>CRC | www.cmostek.com |

| ration Settings OOK Demod<br>aseband2 Settings                                                                                                             | Settings (G)FSK Demod                                                                       | Settings Baseband 1 Setting                                             | -0x00                                                                     | Variable         |             |                 |

| ration Settings OOK Demod<br>aseband2 Settings                                                                                                             | Settings (G)FSK Demod                                                                       | Settings Baseband 1 Settin<br>0x1234<br>Sync                            | -0x00                                                                     | Variable         | CRC         |                 |

| ration Settings OOK Demod<br>aseband2 Settings<br>Packet Type<br>Variable Length *                                                                         | Settings (G)FSK Demod :<br>OxAA<br>Preamble                                                 | Settings Baseband 1 Settin<br>0x1234<br>Sync                            | 0x00                                                                      | Variable Data    | CRC         |                 |

| ration Settings OOK Demod<br>aseband2 Settings<br>Packet Type<br>Variable Length *<br>Node-Length Position                                                 | Settings (G)FSK Demod :<br>OxAA<br>Preamble<br>Node Id Size                                 | Settings Baseband 1 Settin<br>Ox1234<br>Sync<br>V Hex Noc<br>Dec        | 0x00 1 byte-<br>Node ID Length<br>Ie Id Value (0-0xFF)                    | Variable Data    | CRC<br>Mode |                 |

| ration Settings OOK Demod<br>aseband2 Settings<br>Packet Type<br>Variable Length *<br>Node-Length Position<br>First Node, then Len! *                      | Settings (G)FSK Demod :<br>OxAA<br>Preamble<br>Node Id Size<br>1-byte •                     | Settings Baseband 1 Settin<br>Ox1234<br>Sync<br>V Hex Noc<br>Dec<br>Noc | 0x00                                                                      | Variable Data    | CRC<br>Mode | List            |

| ration Settings OOK Demod<br>aseband2 Settings<br>Packet Type<br>Variable Length *<br>Node-Length Position<br>First Node, then Len; *<br>Payload Bit Order | Settings (G)FSK Demod :<br>OxAA<br>Preamble<br>Node Id Size<br>1-byte •<br>Node Id Err Mask | Settings Baseband 1 Settin<br>Ox1234<br>Sync<br>V Hex Noc<br>Dec<br>Noc | 0x00 1 byte-<br>Node ID Length<br>le Id Value (0-0xFF)<br>0<br>le Id Free | Variable Data    | CRC<br>Mode | List            |

# Figure 8. Packet RFPDK Interface

| Register Bit RFPDK Parameter                                    | Register Bit       |

|-----------------------------------------------------------------|--------------------|

| Packet Type                                                     | PKT_TYPE           |

| Calculate synthetically according to each parameter. The        | PAYLOAD_LENG<10:0> |

| specific method is described below.                             |                    |

| Node-Length Position                                            | NODE_LENG_POS_SEL  |

| Payload Bit Order                                               | PAYLOAD_BIT_ORDER  |

| No input in RFPDK. You can use it flexibly in applications, The | AUTO_ACK_EN        |

| introduction is below.                                          |                    |

| Register<br>Name    | Bits | R/W | Bit Name           | Function Description                                                                                                                                                                                                                                                                     |

|---------------------|------|-----|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | 6:4  | RW  | PAYLOAD_LENG<10:8> | The <10:8> bit of the 11-bit Payload length.<br>When PKT_TYPE is set as a fixed length<br>packet, the configurable content is 0-2047,<br>referring to 1-2048 bytes.<br>When PKT_TYPE is set to a variable<br>packet, only <7:0> is valid, and the<br>configurable length is 1-256 bytes. |

| CUS_PKT14           | 3    | RW  | AUTO_ACK_EN        | Automatic packaging the ACK data packets<br>enable.<br>0: Disable<br>1: Enable                                                                                                                                                                                                           |

| (0x45)              | 2    | RW  | NODE_LENG_POS_SEL  | In variable packets, the position relationship<br>between Node ID and Length Byte<br>0: Node ID is before length Byte.<br>1: Node ID is after length Byte.                                                                                                                               |

|                     | 1    | RW  | PAYLOAD_BIT_ORDER  | <ul><li>0: First code and decode each byte MSB of<br/>the payload+CRC.</li><li>1: First code and decode each byte LSB of<br/>the payload+CRC</li></ul>                                                                                                                                   |

|                     | 0    | RW  | PKT_TYPE           | Packet length type<br>0: Fixed packet length<br>1: Variable packet length                                                                                                                                                                                                                |

| CUS_PKT15<br>(0x46) | 7:0  | RW  | PAYLOAD_LENG<7:0>  | The <7:0> bit of the 12-bit Payload length.<br>The explain is as above.。                                                                                                                                                                                                                 |

Table 13. Register Located in Configuration Bank

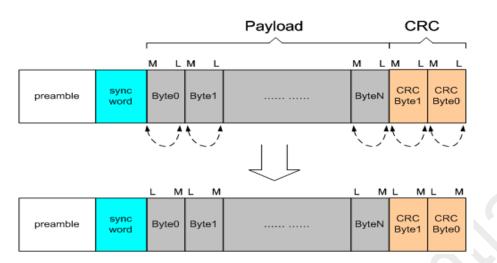

The following explains in detail the meaning of PAYLOAD\_BIT\_ORDER.

PAYLOAD\_BIT\_ORDER = 1 indicates that when sending, each byte itself of Payload and CRC is sent from LSB to MSB in sequence or Manchester/Whiten encoded. On the other hand, the MSB and LSB sequence of each byte itself of the decoded Payload and the CRC must be changed when receiving, and then encode CRC again. If the configuration of RX and TX is the same, the user is unable to see the process. If users use our product to connect with other people's product, they need to understand the process and configure it properly.

PAYLOAD\_BIT\_ORDER = 0 indicates that this operation is not available.

# Figure 9. PAYLOAD\_BIT\_ORDER Operation

Explain AUTO\_ACK\_EN usage in detail below.

CMT2300A's AUTO ACK function does not mean that after receiving a packet, it automatically switches back to the TX mode and send back the ACK packet. This control mode is not supported within the chip. The actual usage is that when MCU sets AUTO\_ACK\_EN to 1, the data packet format is automatically configured as the ACK packet format within the chip, as follows:

Figure 10. ACK Packet Format

This packet only contains Preamble and Sync ID. Then, the external MCU needs to switch the chip to TX mode for sending. The sending content is the packet above. After the sending is completed, MCU needs to set AUTO\_ACK\_EN to 0 first and then perform other operations.

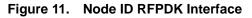

#### 2.5 Node ID Configuration

The corresponding RFPDK interface and parameters are as below:

|                                                         | OxAA-                                    | -0x1234 | 0x00-                              | 1 byte | Variable | None       |     |

|---------------------------------------------------------|------------------------------------------|---------|------------------------------------|--------|----------|------------|-----|

| Packet Type                                             | Preamble                                 | Sync    | Node ID                            | Length | Data     | CRC        | Lis |

| First Node, then Len:  Payload Bit Order Start from msb | 1-byte •<br>Node Id Err Mas<br>Disable • | ]       | Dec 0<br>Node Id Free<br>Disable * |        | Dete     | ct Node ID | Bur |

| Register Bit RFPDK Parameter | Register Bit       |

|------------------------------|--------------------|

| Node Id Size                 | NODE_SIZE<1:0>     |

| Node Id Mode                 | NODE_DET_MODE<1:0> |

| Node Id Value                | NODE_VALUE<31:0>   |

| Node Id Err Mask             | NODE_ERR_MASK      |

| Node Id Free                 | NODE_FREE_EN       |

# Table 14. Node ID Related Parameter

#### Register R/W Bits **Bit Name Function Description** Name In RX mode, the enable bit that makes the Node ID detection circuit independent. 5 RW NODE\_FREE\_EN 0: Disable 1: Enable The Node ID detection error will output a PKT\_ERR interrupt and simultaneously synchronize the reset decoding circuit. The bit 4 RW NODE\_ERR\_MASK controls whether the synchronous reset is performed. 0: Permit the synchronous reset. 1: No permit the synchronous reset. Node ID length: 0: 1 byte CUS\_PKT16 RW 3:2 NODE SIZE<1:0> 1: 2 bytes (0x47) 2: 3 bytes 3: 4 bytes Node ID detection mode: 0: No detection 1: The TX mode sends the contents of the NODE\_VALUE; the RX mode only recognizes the content of the NODE VALUE. 2: The TX mode sends the contents of the RW NODE\_DET\_MODE<1:0> 1:0 NODE VALUE; the RX mode only recognizes the content of the NODE\_VALUE and all 0. 3: The TX mode sends the contents of the NODE\_VALUE; the RX mode only recognizes the content of the NODE\_VALUE, all 0 and all 1. CUS\_PKT17 32-bit Node ID value 7:0 RW NODE\_VALUE<7:0> (0x48) CUS\_PKT18 7:0 RW NODE\_VALUE<15:8>

# Table 15. Register Located in Configuration Bank

| (0x49)              |     |    |                   |

|---------------------|-----|----|-------------------|

| CUS_PKT19<br>(0x4A) | 7:0 | RW | NODE_VALUE<23:16> |

| CUS_PKT20<br>(0x4B) | 7:0 | RW | NODE_VALUE<31:24> |

|           | NODE_VALUE   |              |              |              |  |

|-----------|--------------|--------------|--------------|--------------|--|

| NODE_SIZE | <31:24>      | <23:16>      | <15:8>       | <7:0>        |  |

| 0         | $\checkmark$ |              |              |              |  |

| 1         | $\checkmark$ | $\checkmark$ |              |              |  |

| 2         | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |  |

| 3         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

The tick in the table indicates the register to be filled in. For example, if the NODE\_SIZE is set to 1, that is, the length is 2 byte and the value is 0x5678, the user will fill the value in the two registers of SYNC\_VALUE<31:24> and SYNC\_VALUE<23:16>. The MSB corresponds to the thirty-first bit. The LSB corresponds to the sixteenth bit. That is filling 0x56 into SYNC\_VALUE<31:24> and filling 0x78 into SYNC\_VALUE<23:16>.

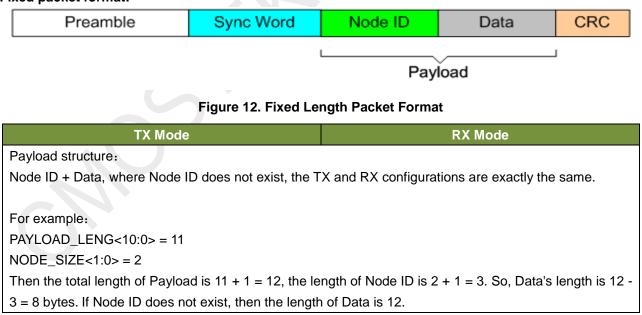

The following will introduce, in different PKT\_TYPE, how to set up PAYLOAD\_LENG and NODE\_SIZE, how to confirm the DATA length inside Payload, how to explain the Length Byte meaning. Users can find the parts they need to understand in the following table as needed:

#### Fixed packet format:

# Variable packet format:

# Condition 1: Node ID does not exist

# Figure13. Variable Packet Format, Node ID does not exist

| TX Mode                                                                          | RX Mode                      |

|----------------------------------------------------------------------------------|------------------------------|

| Payload structure:                                                               | Payload structure:           |

| Length Byte + Data                                                               | Length Byte + Data           |

|                                                                                  |                              |

| Payload length:                                                                  | Length Byte content          |

| 1 + PAYLOAD_LENG<7:0>, where the content of PAYLOAD_LENG<7:0>                    | meaning:                     |

| is equal to the content of Length Byte, which refers to the Data length          | Represents that the followed |

| followed, and therefore can only fill 8 bits, the maximum value is 255. The      | Data length corresponds to   |

| previous 1 represents the Length Byte itself is the length of the 1 byte.        | the TX configuration.        |

|                                                                                  |                              |

| For example:                                                                     |                              |

| PAYLOAD_LENG<7:0> = 11,                                                          |                              |

| then the total length of Payload is $1 + 11 = 12$ , so the length of Data is 11. |                              |

# Condition 2: Node ID exists, and NODE\_POSITION = 0 (Node ID is before Length Byte.)

| Preamble | Sync Word | Node ID | Length | Data | CRC |

|----------|-----------|---------|--------|------|-----|

|          | I         |         | ~      |      | I   |

Payload/CRC

# Figure 14. Variable packet format, Node ID exists, Node ID is before Length Byte

| TX Mode                                              | RX Mode                                  |

|------------------------------------------------------|------------------------------------------|

| Payload structure:                                   | Payload structure:                       |

| Node ID + Length Byte + Data                         | Node ID + Length Byte + Data             |

|                                                      |                                          |

| Payload length:                                      | Length Byte content meaning:             |

| (NODE_SIZE+1) + 1 + PAYLOAD_LENG<7:0>,               | Represents that the followed Data length |

| where the content of PAYLOAD_LENG<7:0> is            | corresponds to the TX configuration.     |

| equal to the content of Length Byte, which refers to |                                          |

| the length of the Data followed, and therefore can   |                                          |

| only fill 8 bits, the maximum value is 255. The      |                                          |

| middle plus 1 means the Length Byte itself is the    |                                          |

| length of the 1 byte.                                |                                          |

| For example:           |                                  |

|------------------------|----------------------------------|

| PAYLOAD_LENG<7:        | 0> = 11,NODE_SIZE<1:0> =         |

| 2, then the total len  | igth of Payload is (2 + 1) + 1 + |

| 11 = 15, so the length | n of Data is 11.                 |

### Condition 3: Node ID exists, and NODE\_POSITION = 1 (Node ID is after Length Byte.)

| Preamble | Sync Word | Length | Node ID | Data | CRC |

|----------|-----------|--------|---------|------|-----|

|          |           | L      |         |      | 1   |

Payload/CRC

# Figure 15. Variable Packet Format, Node ID Exists, Node ID is after Length Byte

| TX Mode                                                                      | RX Mode                      |

|------------------------------------------------------------------------------|------------------------------|

| Payload structure:                                                           | Payload structure:           |

| Length Byte + Node ID + Data                                                 | Length Byte + Node ID +      |

| Payload length:                                                              | Data                         |

| 1 + PAYLOAD_LENG<7:0>, where the content of PAYLOAD_LENG<7:0>                |                              |

| is equal to the content of Length Byte, which refers to the following Node   | Length Byte content          |

| ID plus the length of Data, so it can only fill 8 bits, the maximum value is | meaning:                     |

| 255. The previous 1 means the Length Byte itself is the length of the 1      | Represents that the followed |

| byte.                                                                        | length of Node ID + Data     |

|                                                                              | corresponds to the TX        |

| For example:                                                                 | configuration.               |

| PAYLOAD_LENG<7:0> = 11, NODE_SIZE<1:0> = 2, then the total length            |                              |

| of Payload is $1 + (2 + 1) + 8 = 12$ , so the length of Data is 8.           |                              |

# 2.6 FEC Configuration

The corresponding RFPDK interface and parameters are as below:

| peration Settings   | OOK Demod Settings | (G)FSK Demod Settings B | Baseband 1 Settings Baseband 2 Settings | Feature Settings      |                 |

|---------------------|--------------------|-------------------------|-----------------------------------------|-----------------------|-----------------|

| Baseband Setting    |                    |                         |                                         |                       |                 |

| Data Mode<br>Packet |                    |                         |                                         |                       |                 |

|                     |                    |                         |                                         |                       | List            |

| Whitening           |                    | Whiten Type             | Whiten Seed Type                        | Whiten Seed (0-511)   |                 |

| Disable             | *                  | NA -                    | NA -                                    | NA                    | Export          |

| Mancheste           | er                 | Manchester Type         | FEC                                     | FEC Type              |                 |

| Disable             | •                  | NA *                    | Enable                                  | x^3+x+1 *             | Burn            |

| Tx Prefix T         | уре                | Tx Packet Number (1-2   | 256) Tx Packet Gap (2-256)              | Fifo Threshold (1-31) |                 |

| 0                   | ×                  | 1                       | 32                                      | 16                    |                 |

| ana ana an          |                    |                         |                                         |                       |                 |

| USB:Unconnected     | d O Device: U      | nknown Notice:          |                                         |                       | www.cmostek.com |

#### Table 16. FEC Related Parameter

| Register Bit RFPDK Parameter | Register Bit |

|------------------------------|--------------|

| FEC                          | FEC_EN       |

| FEC_Type                     | FEC_TYPE     |

#### Table 17. Register Located in Configuration Bank

| Register<br>Name    | Bits | R/W | Bit Name | Function Description                                                                                                          |

|---------------------|------|-----|----------|-------------------------------------------------------------------------------------------------------------------------------|

| CUS_PKT21<br>(0x4C) | 7    | RW  | FEC_TYPE | Polynomial selection of FEC (7,4) encoding<br>and decoding:<br>0: the polynomial is x^3+x+1<br>1: the polynomial is x^3+x^2+1 |

| (0,40)              | 6    | RW  | FEC_EN   | FEC (7,4) encoding and decoding enable:<br>0: Disable<br>1: Enable                                                            |

The main function of FEC is to correct an erroneous data in the packet, so it can reduce the packet error rate.

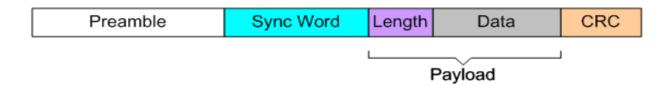

#### 2.7 CRC Configuration

#### The corresponding RFPDK interface and parameters are as below:

| E                    | OxAA             | 0x1234 | 0x00               |       | CCITT-16      |      |

|----------------------|------------------|--------|--------------------|-------|---------------|------|

| Packet Type          | Preamble         | Sync   | Node ID            | Data  | CRC           | List |

| Fixed Length         |                  |        | CRC Ran            | ge    |               |      |

| Node-Length Position | Crc Options      |        | Crc Seed (0-65535) | Crc R | ange          | Expo |

| NA -                 | CCITT-16 -       |        | 0                  | Entir | e Payload 👻   |      |

| Payload Bit Order    | Crc Swap         | ,      | Crc Bit Inv        | Crc B | it Order      | Bun  |

| Start from msb 💌     | Start From MSB 💌 | ]      | Normal             | Start | From bit 15 💌 |      |

| Start from msb *     | Start From MSB   |        | Normal             | Start | From Dit 15   |      |

# Figure 17. CRC RFPDK Interface

#### Table18. CRC Related Parameter

| Register Bit RFPDK Parameter                 | Register Bit   |

|----------------------------------------------|----------------|

| Crc Options                                  | CRC_TYPE<1:0>  |

| Crc Seed                                     | CRC_SEED<15:0> |

| Crc Options 为 None 时,CRC_EN = 0,否则 CRC_EN =1 | CRC_EN         |

| Crc Range                                    | CRC_RANGE      |

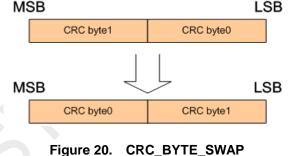

| Crc Swap                                     | CRC_BYTE_SWAP  |

| Crc Bit Inv                                  | CRC_BIT_INV    |

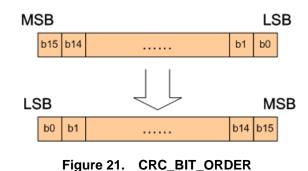

| Crc Bit Order                                | CRC_BIT_ORDER  |

| Register<br>Name    | Bits | R/W | Bit Name       | Function Description                                                                                                                                                                                                                   |

|---------------------|------|-----|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | 5    | RW  | CRC_BYTE_SWAP  | CRC send-receive order:<br>0: First send and receive the high byte<br>1: First send and receive the low byte                                                                                                                           |

|                     | 4    | RW  | CRC_BIT_INV    | <ul><li>Whether or not CRC code is reversed.</li><li>0: CRC code is not reversed.</li><li>1: CRC code is reversed bit by bit.</li></ul>                                                                                                |

| CUS_PKT21           | 3    | RW  | CRC_RANGE      | CRC calculation range:<br>0: the whole payload<br>1: only for data                                                                                                                                                                     |

| (0x4C)              | 2:1  | RW  | CRC_TYPE<1:0>  | CRC polynomial type:<br>0:CCITT-16<br>1:IBM-16<br>2:ITU-16(equals the reversed CCITT-16)<br>3: NA                                                                                                                                      |

|                     | 0    | RW  | CRC_EN         | CRC enable<br>0: Disable<br>1: Enable                                                                                                                                                                                                  |

| CUS_PKT22<br>(0x4D) | 7:0  | RW  | CRC_SEED<7:0>  | Initial values of CRC polynomial                                                                                                                                                                                                       |

| CUS_PKT23<br>(0x4E) | 7:0  | RW  | CRC_SEED<15:8> |                                                                                                                                                                                                                                        |

| CUS_PKT24<br>(0x4F) | 7    | RW  | CRC_BIT_ORDER  | <ul> <li>CRC Big-end and Little-end order</li> <li>configuration:</li> <li>0: CRC bytes send and receive in order from</li> <li>bit15 to bit0.</li> <li>1: CRC bytes send and receive in order from</li> <li>bit0 to bit15.</li> </ul> |

Table 19. Register Located in Configuration Bank

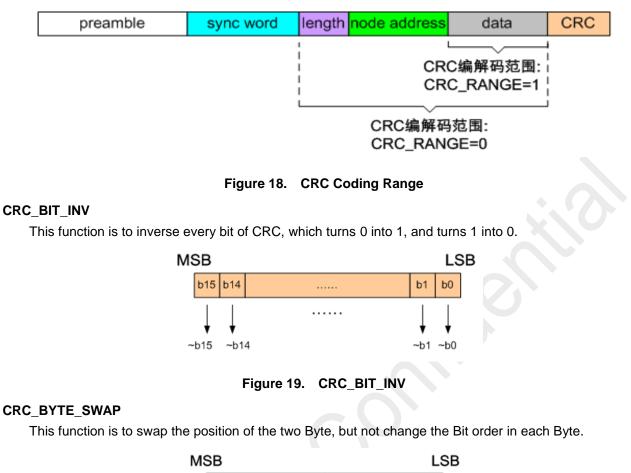

The following explains in detail the principles of several configurations of CRC.

# CRC\_RANGE

This function is the codec checksum object of the specified CRC. It could be the whole Payload, or the Data part.

# CRC\_BIT\_ORDER

This function is to reverse the high and low order of the whole CRC. If the position of the two BYTE is changed, it will be inverted according to the high and low order after the change.

#### 2.8 Codec Configuration

The corresponding RFPDK interface and parameters are as below:

| peration Settings | OOK Demod Settings | (G)FSK Demod Settings Base | eband 1 Settings | Baseband 2 Settings | Feature Settings     |                 |

|-------------------|--------------------|----------------------------|------------------|---------------------|----------------------|-----------------|

| Baseband Setting  | gs                 |                            |                  |                     |                      |                 |

| Data Mode         | <u> </u>           |                            |                  |                     |                      |                 |

| Packet            | *                  |                            |                  |                     |                      | List            |

| Whitening         |                    | Whiten Type                | w                | hiten Seed Type     | Whiten Seed (0-511)  |                 |

| Enable            | *                  | PN9 CCITT                  |                  | Type 1              | 0                    | Export          |

| Mancheste         | er                 | Manchester Type            | FE               | c                   | FEC Type             |                 |

| Disable           |                    | NA *                       |                  | Enable *            | x^3+x+1 -            | Burn            |

| Tx Prefix T       | уре                | Tx Packet Number (1-256    | i) Ta            | Packet Gap (2-256)  | Fifo Threshold (1-31 | )               |

| 0                 | *                  | 1                          |                  | 32                  | 16                   |                 |

| USB:Unconnected   | d 🕘 Device: U      | nknown Notice:             |                  |                     | í.                   | www.cmostek.com |

Figure 22. Codec RFPDK Interface

| Figure 22. Codec RFPDK Interface |                  |  |  |  |  |  |  |

|----------------------------------|------------------|--|--|--|--|--|--|

| Table 20. Codec Related P        | Parameter        |  |  |  |  |  |  |

| Register Bit RFPDK Parameter     | Register Bit     |  |  |  |  |  |  |

| Whitening                        | WHITEN_EN        |  |  |  |  |  |  |

| Whiten Type                      | WHITEN_TYPE<1:0> |  |  |  |  |  |  |

| Whiten Seed Type                 | WHITEN_SEED_TYPE |  |  |  |  |  |  |

| Whiten Seed                      | WHITEN_SEED<8:0> |  |  |  |  |  |  |

| Manchester                       | MANCH_EN         |  |  |  |  |  |  |

| Manchester Type                  | MANCH_TYPE       |  |  |  |  |  |  |

| Table 20. | Codec | Related | Parameter |

|-----------|-------|---------|-----------|

|           |       |         |           |

|                     |      |     |                  | 5                                                                                                                                                                                             |

|---------------------|------|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|